Publish Date: July 30, 2021

IIT Delhi Researcher in Collaboration with NUS Designs Device for High Density Magnetic Memory

Share this on

- Proposed device to help in reducing frequent charging of wireless electronic devices such as mobile phone, IoT devices

New Delhi: As we are moving toward a data-driven age, there is a need for faster and very low power computing. Memories play a crucial role in this, as for faster processing of data, the CPU rapidly reads and writes on the memory.

The main memory, i.e., the Random-access memories (RAMs), are most commonly used in modern computer architecture. These are SRAMs and DRAMs, which are based on CMOS technology. They are fast but volatile, which means they require a constant supply of power, this consumes lots of energy. But if these could be made non-volatile, then computing could be made more energy efficient.

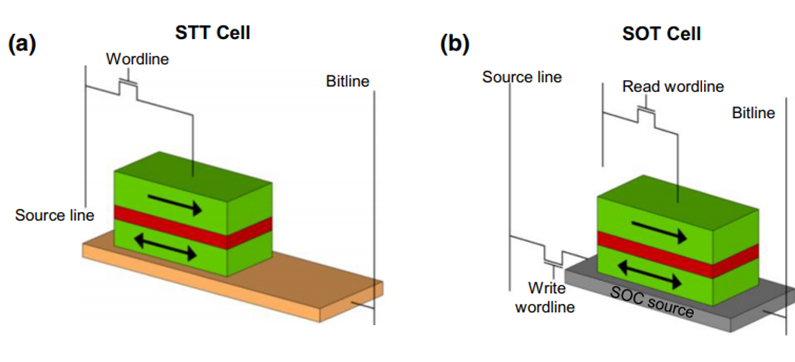

Spintronics memories like spin-transfer torque magnetoresistive RAM (STT-MRAM) and spin-orbit torque magnetoresistive RAM (SOT-MRAM) are inherently non-volatile. They consume no power at standby. Also, their operation speeds are comparable to RAMs. Hence, these spintronics memories are the most potential candidates for replacing current electronic RAMs.

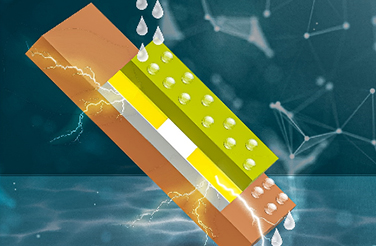

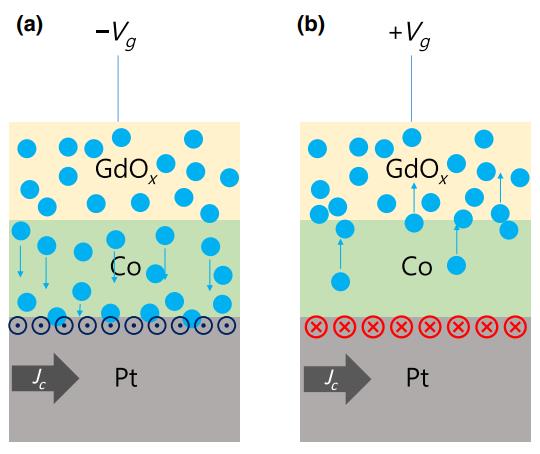

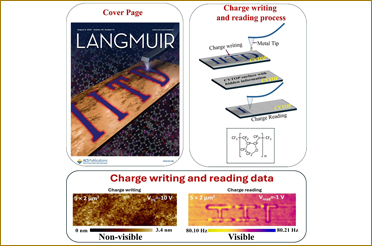

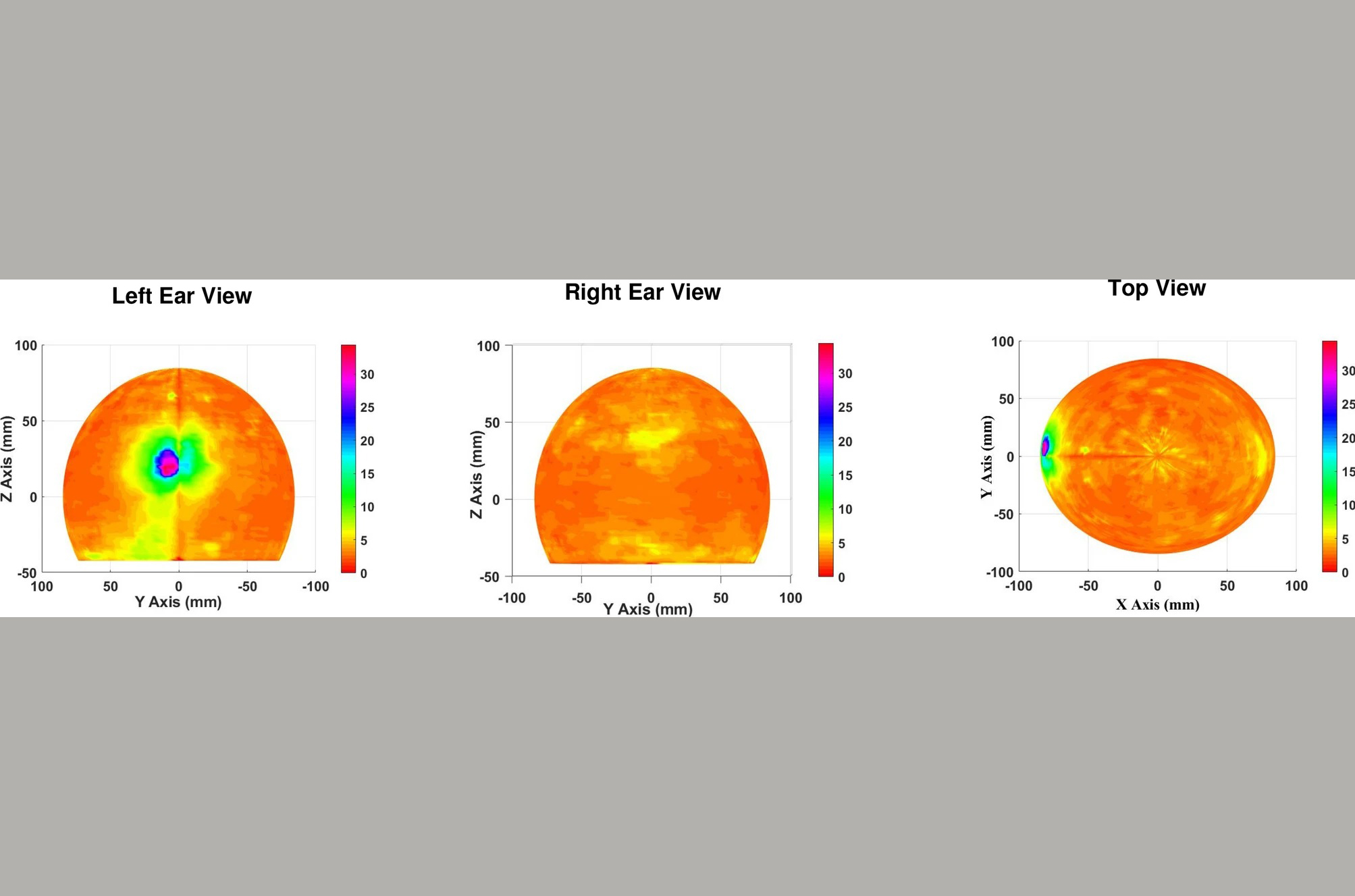

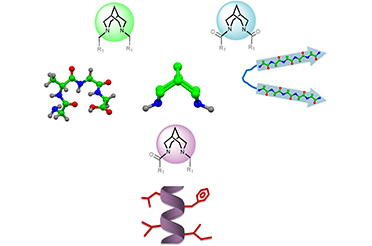

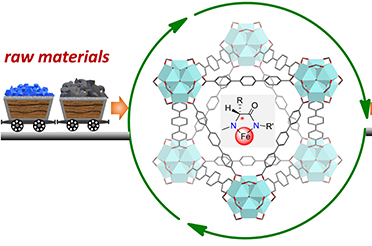

Figure 1 Spintronics memories

SOT-MRAMs are better than STT-MRAM in terms of reliability and writing speed but lags behind in achieving high integration density. This is because, unlike STT-MRAM, which is a two-terminal device and needs one transistor for reading and writing operation, the SOT-MRAMs requires two transistors each for reading and writing. Thus SOT-MRAM requires a larger area per bit as compared to STT-MRAM, as shown in figure 1.

Also, SOT-MRAM is less prone to breakdown due to separate read and write paths, this is absent in STT-MRAMs. Hence, SOT-MRAM is the preferred choice among the research community however significant work is required to increase their areal density.

In a collaborative work between Prof. Rahul Mishra from the Centre for Applied Research in Electronics (CARE), IIT Delhi and Prof. Hyunsoo Yang from the National University of Singapore (NUS) a possible solution for achieving higher integration density in SOT-MRAMs was proposed and experimentally demonstrated.

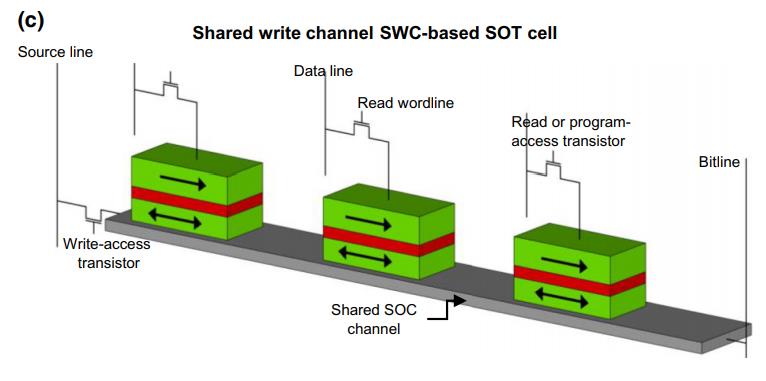

Prof. Rahul Mishra, CARE, IIT Delhi said, “We demonstrated a shared write channel based multibit SOT cell scheme, which reduces the number of transistors required per bit. This cell design requires half the area compared to conventional SOT MRAM, thus almost doubles the area efficiency of the memory chip”.

The below figure represents the basic idea and schematic of a shared channel SOT-MRAM.

Figure 2- Shared channel scheme for increasing the area efficiency

To make the above design feasible, the team designed a magnetic memory device, which can be programmed by application of gate voltage. The gate voltage was used to migrate oxygen ions in the device, which resulted in modulation of the spin current polarity as shown in the Figure 3. Thus, cells can now be written individually, and hence they obtained a full-fledged, working area-efficient SOT memory. The work was published in Physical Review applied (https://journals.aps.org/prapplied/abstract/10.1103/PhysRevApplied.15.024063)

Prof. Mishra further said, “The results of this work could eventually help to develop low power electronic devices. The frequent charging of wireless electronic devices such as mobile phone, IoT devices, etc would be significantly reduced with the proposed device. It would be especially useful for industrial applications where sensors are put in locations, which are not easy to access. Low power and high-density memory devices would not only be helpful in reducing global energy footprint, but the saved energy can also be used for extra computational tasks”.

Figure 3- Working principle of the proposed device

**********

Other News

IIT Delhi Celebrates ‘Jai Bhim Saptaha 2026’: A Week of Reflection, Dialogue, and Participation Commemorating the Legacy of Dr. B.R. Ambedkar

Read More

आई.सी.ई.एफ. रिपोर्ट : आई.आई.टी. दिल्ली के शोधार्थियों द्वारा भारत के ऊर्जा संक्रमण के संरचनात्मक और सामाजिक-आर्थिक अध्ययन पर जोर

Read More

ICEF Report: IIT Delhi Researchers Call for Examining Systemic and Socio-Economic Dimensions of India's Energy Transition

Read More

फ्लिपकार्ट के सह-संस्थापक और आई.आई.टी. दिल्ली के पूर्व विद्यार्थी बिन्नी बंसल द्वारा संस्थान में उनके नाम पर रखे गए एक प्रदर्शनी हॉल का उद्घाटन

Read More

Flipkart Co-founder and IIT Delhi Alum Binny Bansal Inaugurates an Exhibition Hall Named After Him at the Institute

Read More

क्यू.एस. विषय रैंकिंग 2026: आई.आई.टी. दिल्ली पांच प्रमुख विषयों में दुनिया के शीर्ष 50 में; भारत के शीर्षतम इंजीनियरी एवं प्रौद्योगिकी संस्थान के रूप में कायम

Read More

QS Subject Rankings 2026: IIT Delhi in Global Top 50 in Five Major Subjects, Continues as the No. 1 Engineering & Technology Institute in India

Read More

Alumnus Anant Yardi Pledges Transformational Gift to Strengthen AI Leadership and Campus Infrastructure at IIT Delhi | आई.आई.टी. दिल्ली में ए.आई. नेतृत्व और परिसर अवसंरचना के सुदृढ़ीकरण की दिशा में पूर्व विद्यार्थी अनंत यार्डी का दूरदर्शी योगदान।

Read More

IIT Delhi’s DMSE Launches First-of-its-Kind Comic Book–Style Brochure to Demystify Complex Scientific Concepts | आई.आई.टी. दिल्ली के पदार्थ विज्ञान एवं इंजीनियरी विभाग ने अपनी तरह की पहली कॉमिक बुक शैली का ब्रोशर लॉन्च किया

Read More

Mercedes-Benz Research and Development India and IIT Delhi Collaborate for Joint Research | मर्सिडीज‑बेंज रिसर्च एंड डेवलपमेंट इंडिया और आई.आई.टी. दिल्ली ने संयुक्त अनुसंधान के लिए साझेदारी की

Read More

IIT Delhi to Organise Anveshan 2026 for Final-Year UG and PG Students on March 21 | आई.आई.टी. दिल्ली स्नातक (यू.जी.) और स्नातकोत्तर (पी.जी.) के अंतिम वर्ष के विद्यार्थियों के लिए 21 मार्च को “अन्वेषण 2026” का आयोजन करेगा

Read More

ISA and IIT Delhi Deepen Partnership to Advance Solar Skills Across Member Countries | आई.एस.ए. (ISA) और आई.आई.टी. दिल्ली ने सदस्य देशों में सौर कौशल को बढ़ावा देने की दिशा में की मजबूत साझेदारी

Read More

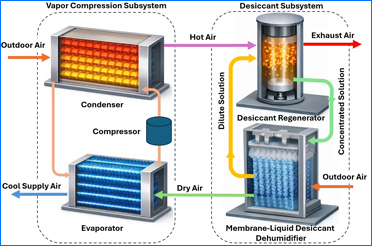

IIT Delhi Researchers Developing a High-Efficiency AC Capable of Reducing Electricity Use by a Third | आई.आई.टी. दिल्ली के शोधार्थी कर रहे हैं बिजली-बचत वाला स्मार्ट एयर कंडीशनर विकसित

Read More

IIT Delhi Signs MoU with Jindal Steel to Establish Nodal Centre of Excellence for Structural Steel Research and Innovation | संरचनात्मक स्टील अनुसंधान में नया कदम: आई.आई.टी. दिल्ली ने जिंदल स्टील के साथ समझौता ज्ञापन पर किया हस्ताक्षर

Read More

IIT Delhi Join Hands with SAI, UK’s Exeter University for a Training Program in Sports Technology | खेल प्रौद्योगिकी प्रशिक्षण के लिए आई.आई.टी. दिल्ली ने की भारतीय खेल प्राधिकरण और एक्सेटर विश्वविद्यालय (यू.के.) के साथ साझेदारी

Read More

Union Minister for Education Shri Dharmendra Pradhan Lays Foundation Stones for Academic Block and Girls Hostel at IIT Delhi | केंद्रीय शिक्षा मंत्री श्री धर्मेंद्र प्रधान द्वारा आई.आई.टी. दिल्ली में शैक्षणिक खंड एवं महिला छात्रावास का शिलान्यास

Read More

अ.जा./अ.ज.जा. समुदाय के पीएच.डी. शोधार्थियों के लिए ‘STEMM में परिवर्तनकारी नेतृत्व’ कार्यशाला के तीसरे संस्करण का सफल आयोजन | Third Edition of Transformative Leadership in STEMM Workshop for Ph.D. Scholars from SC/ST Community Held

Read More

उद्यमिता विकास प्रकोष्ठ (eDC), आई.आई.टी. दिल्ली द्वारा BECon’26 का आयोजन | Entrepreneurship Development Cell (eDC), IIT Delhi to Organise BECon’26, One of India’s Largest Student-Led Entrepreneurship Summits

Read More

आई.आई.टी. दिल्ली ने मनाया अपना 68वां स्थापना दिवस: 'अल्युमनी इम्पैक्ट रिपोर्ट' की गई जारी | IIT Delhi Celebrates its 68th Foundation Day, Releases Alumni Impact Report

Read More

आई.आई.टी. दिल्ली के #एक्सपीरियंसआईआईटीडी के तहत जे.ई.ई. 2026 के अभ्यर्थियों के लिए कोटा, राजस्थान में ओपन हाउस का आयोजन | IIT Delhi to Organise Open House for JEE 2026 Aspirants in Kota, Rajasthan, Under its Flagship Outreach Initiative #ExperienceIITD

Read More

आई.आई.टी. दिल्ली ने युवा संकायों को शोध में सशक्त बनाने के लिए की दीपक राघवन फैमिली फाउंडेशन एक्सेलरेटर कार्यक्रम की शुरुआत | IIT Delhi Launches Deepak Raghavan Family Foundation Accelerator Program to Strengthen Young Faculty in Research

Read More

आई.आई.टी. दिल्ली में नासा एस्ट्रोनॉट सुनीता विलियम्स का व्याख्यान: ‘द मेकिंग ऑफ एन एस्ट्रोनॉट: सुनीता विलियम्स स्टोरी' | NASA Astronaut Sunita Williams Delivers a Talk at IIT Delhi: 'The Making of an Astronaut: Sunita Williams' Story’

Read More

आई.आई.टी. दिल्ली ने समावेशिता को दिया बढ़ावा, इंटर-कॉलेज समावेशी खेल समारोह 'SANGAM 2026' का सफल समापन | IIT Delhi Champions Inclusion as Inter-College Inclusive Sports Meet ‘SANGAM 2026’ Concludes Successfully

Read More

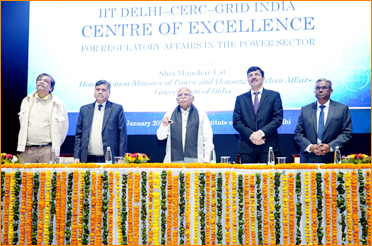

आई.आई.टी. दिल्ली में विद्युत क्षेत्र में विनियामक मामलों के लिए उत्कृष्टता केंद्र का शुभारंभ | Centre of Excellence for Regulatory Affairs in the Power Sector Launched at IIT Delhi

Read More

आई.आई.टी. दिल्ली ने हाइली इन्फेक्शियस पैथोजेन्स से संबंधित अनुसंधान को बढ़ावा देने के लिए बायोसेफ्टी लेवल 3 अनुसंधान सुविधा आरंभ

Read More

आई.आई.टी. दिल्ली और वाधवानी फाउंडेशन द्वारा वाधवानी इनोवेशन नेटवर्क के अंतर्गत सेंटर फॉर एक्सीलेंस इन प्रिसीजन एन्ड पर्सनलाइज़्ड हेल्थकेयर का उद्घाटन

Read More

आई.आई.टी. दिल्ली का 56वाँ दीक्षांत समारोह: 2764 छात्रों को डिग्री व डिप्लोमा, मुख्य अतिथि भारत की मिसाइल वुमन डॉ. टेसी थॉमस का प्रेरणादायी संबोधन

Read More

डिज़ाइन फ़ॉर भारत – यूथ इनोवेशन चैलेंज 2026’ के अंतर्गत आई.आई.टी. दिल्ली में एक डिज़ाइन प्रदर्शनी का आयोजन | A Design Exhibition Under Design for Bharat—Youth Innovation Challenge 2026 Held at IIT Delhi

Read More

आई.आई.टी. दिल्ली के शैक्षणिक सत्र 2000 के विद्यार्थियों द्वारा संस्थान को रु. 70 करोड़ से अधिक के दान की घोषणा

Read More

आई.आई.टी दिल्ली द्वारा ओपन हाउस का आयोजन; विद्यार्थियों, उद्योग जगत तथा फंडिंग एजेंसियों के समक्ष अत्याधुनिक अनुसंधान एवं नवाचार परियोजनाओं का प्रदर्शन

Read More

आई.आई.टी. दिल्ली के टेक्नॉलजी इनोवेशन हब आई.एच.एफ.सी. द्वारा स्टार्टअप्स के लिए प्रमुख पिचिंग पहल ‘पिच परफेक्ट 2.0’ का शुभारंभ

Read More

आई.आई.टी. दिल्ली–अबू धाबी में शिक्षा मंत्री श्री धर्मेंद्र प्रधान द्वारा प्रमुख कार्यक्रमों एवं स्टार्टअप इनक्यूबेटर का शुभारंभ - ऐतिहासिक द्विपक्षीय साझेदारी को मिली मजबूती

Read More

आई.आई.टी. दिल्ली ने अल्युमनी द्वारा किए गए महत्वपूर्ण योगदान का सम्मान करते हुए अपने प्रदर्शनी हॉल का नाम एलुमनस बिन्नी बंसल के सम्मान में रखने की घोषणा की

Read More

आई.आई.टी. दिल्ली के शोधकर्ताओं द्वारा मानव वैज्ञानिकों की तरह वास्तविक वैज्ञानिक प्रयोग कर सकने वाले कृत्रिम एजेंट 'AILA' का निर्माण

Read More

आई.आई.टी. दिल्ली और एम्स के शोधकर्ताओं ने एक निगलने योग्य सूक्ष्म उपकरण विकसित किया है जो छोटी आंत से सूक्ष्मजीवों के नमूने एकत्र करेगा।

Read More

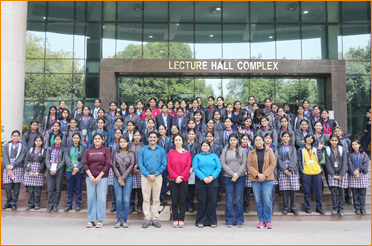

आई.आई.टी. दिल्ली द्वारा आयोजित " हाई स्कूल की छात्राओं के लिए एक एसटीईएम मेंटरशिप कार्यक्रम: मनस्वी (Manasvi)" का चौथा संस्करण सफलतापूर्वक संपन्न

Read More

आई.आई.टी. दिल्ली के अंतर्गत स्थापित केंद्र तकनीकी वस्त्रों, रक्षा श्रेणी के रेशों और राष्ट्रीय ध्वज के पुनर्चक्रण के लिए प्रौद्योगिकियों का हस्तांतरण

Read More

आई.आई.टी. दिल्ली ने उभरती प्रौद्योगिकियों में प्रभावशाली अनुसंधान को बढ़ावा देने के लिए की यामाहा मोटर सॉल्यूशंस इंडिया के साथ साझेदारी

Read More

मांग पक्ष ऊर्जा प्रबंधन के लिए कृत्रिम बुद्धिमत्ता समर्थित स्मार्ट डिवाइस विकसित करने के लिए आई.आई.टी. दिल्ली और पूर्व क्षेत्रीय लोड डिस्पैच सेंटर (ERLDC) ने की साझेदारी

Read More

आई.आई.टी. दिल्ली के बी.टेक. (प्रथम वर्ष) के विद्यार्थियों ने वास्तविक दुनिया की समस्याओं से निपटने के अपने कौशल का किया प्रदर्शन

Read More

उच्च शिक्षा संस्थानों के माध्यम से ग्रामीण भारत को बदलने के लिए “उन्नत भारत अभियान” के सफल 11 वर्ष

Read More

आई.आई.टी. दिल्ली ने विचारपूर्ण श्रद्धांजलि और प्रेरणादायक संवादों के साथ मनाया जनजातीय गौरव दिवस

Read More

आई.आई.टी. दिल्ली अध्ययन: सटीक लोकेशन अनुमति वाले एंड्रॉइड ऐप्स से प्रयोक्तओं की निजी जानकारी हो सकती है उजागर

Read More

केवीएस और आई.आई.टी. दिल्ली ने छात्रों और शिक्षकों के लिए विद्यालयों में STEM शिक्षा को सुदृढ़ करने के लिए एक समझौता ज्ञापन (एमओयू) पर किया हस्ताक्षर

Read More

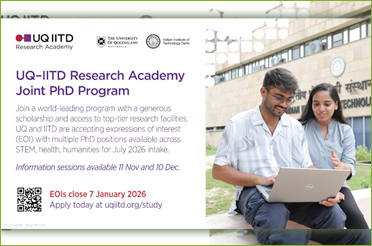

क्वींसलैंड विश्वविद्यालय और आई.आई.टी. दिल्ली द्वारा जुलाई 2026 से शुरू होने वाले सयुंक्त पीएच.डी.

Read More

भारतीय नौसेना के नौसेना वास्तुकला निदेशालय ने आई.आई.टी. दिल्ली के साथ युद्धपोत डिजाइन के चालक दल-केंद्रित पहलुओं के लिए समझौता ज्ञापन पर किया हस्ताक्षर

Read More

श्री लंका के माननीय प्रधानमंत्री डॉ . हरिनी निरेका अमरसूर्या ने किया आई. आई. टी. दिल्ली का दौरा

Read More

आई.आई.टी. दिल्ली के शैक्षणिक सत्र 2000 के विद्यार्थियों द्वारा संस्थान को रु. 70 करोड़ से अधिक के दान की घोषणा | IIT Delhi’s Batch of 2000 Commits Record ₹70+ Crore Pledge at Silver Jubilee Reunion

Read More

IIT Delhi Announces to Name its Exhibition Hall in Honor of Alumnus Binny Bansal, Celebrating Transformative Alumni Giving

Read More

आई.आई.टी. दिल्ली के शोधकर्ताओं द्वारा मानव वैज्ञानिकों की तरह वास्तविक वैज्ञानिक प्रयोग कर सकने वाले कृत्रिम एजेंट 'AILA' का निर्माण | IIT Delhi Researchers Create AI-Agent ‘AILA’ That Can Conduct Real Scientific Experiments Like Human Scientists

Read More

आई.आई.टी. दिल्ली और एम्स के शोधकर्ताओं ने किया एक निगलने योग्य सूक्ष्म उपकरण विकसित | IIT Delhi and AIIMS Researchers Develop a Swallowable Microdevice That Can Collect Microbial Samples from the Small Intestine

Read More

4th Edition of “Manasvi: a STEM Mentorship Program for High School Girls” by IIT Delhi Concludes Successfully

Read More

Centre Set Up Under IIT Delhi Transfers Technologies for Recycling of Technical Textiles, Defence Grade Fibers, and the National Flag

Read More

IIT Delhi Partners with Yamaha Motor Solutions India to Drive Impactful Research in Emerging Technologies

Read More

IIT Delhi and ERLDC Collaborate to Develop AI-Enabled Smart Device for Demand Side Energy Management

Read More

IIT Delhi’s First-Year B.Tech. Students Showcase Their Skills to Tackle Real-World Problems

Read More

Unnat Bharat Abhiyan Completes 11 Successful Years of Transforming Rural India Through Higher Education Institutions

Read More

IIT Delhi Organises Open House; Showcases Cutting-Edge Research and Innovative Projects to Students, Industry, and Funding Agencies

Read More

IIT Delhi’s Technology Innovation Hub IHFC to Launch ‘Pitch Perfect 2.0’ — a Flagship Pitching Initiative for Startups

Read More

IIT Delhi Celebrates Janjatiya Gaurav Divas with Thoughtful Tributes and Inspiring Dialogues

Read More

आईआईटी दिल्ली अध्ययन: एंड्रॉइड ऐप्स से निजी जानकारी उजागर होने का खतरा | Mobile Apps on Android Devices Requiring Precise Location Permissions Can Reveal a Significant Amount of Private Information About Users: Shows IIT Delhi Study

Read More

University of Queensland and IIT Delhi Open Applications for Joint PhD Programme Commencing July 2026

Read More

KVS and IIT Delhi Sign an MoU to Collaborate on Strengthening STEM Education in Schools for Students and Teachers

Read More

Indian Navy’s Directorate of Naval Architecture Signs MoU with IIT Delhi for Crew Centred Aspects of Warship Design

Read More

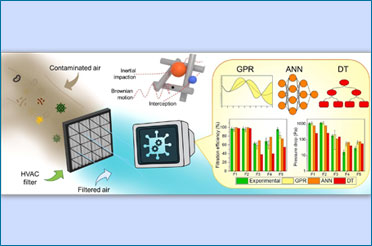

IIT Delhi Researcher-led Team Develops Machine Learning Framework to Design Smarter HVAC Filters to Ensure Healthier Indoor Air Quality

Read More

IHFC, the TIH of IIT Delhi, Showcases 25 Cutting-Edge Technologies to Mark its 5th Anniversary

Read More

Adi Karmayogi Student Chapters Launched at IITs, IIMs, AIIMS, NITs and Top Institutions – Empowering Tribal Youth as Leaders, Innovators, and Change-Makers

Read More

Shri Dharmendra Pradhan, Minister of Education, Inaugurates Key Programs and Startup Incubator at IIT Delhi - Abu Dhabi, Reinforcing a Landmark Bilateral Partnership

Read More

SAI NCSSR and IIT Delhi Sign MoU to Give Impetus to Wider Use of Sports Science and Innovation in India

Read More

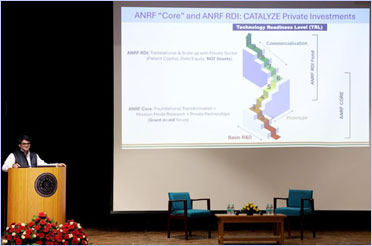

CEO of ANRF Delivers an Insightful Institute Lecture titled “ANRF Vision: Catalyzing India’s Rise as a Research and Innovation Powerhouse” at IIT Delhi

Read More

आई.आई.टी. दिल्ली के शोधार्थियों ने सीमेंट की त्वरित गुणवत्ता जांच के लिए किया एआई मॉडल विकसित | IIT Delhi Researchers Develop AI Models for Instantaneous Quality Check of Cement

Read More

IIT Delhi Inaugurates Biosafety Level 3 Research Facility to Foster Research Involving Highly Infectious Pathogens

Read More

IIT Delhi and Wadhwani Foundation Inaugurate Centre of Excellence in Precision & Personalized Healthcare under Wadhwani Innovation Network

Read More

IIT Delhi Researchers Develop Method to Recycle Denim Waste to Knitted Garments Without Compromising Quality

Read More

Union Minister of Textiles Launches Report on Handloom Carbon Footprint Assessment Prepared by IIT Delhi and DC (Handlooms)

Read More

56th Convocation: 2764 IIT Delhi Students Awarded Degrees and Diplomas; Chief Guest Dr. Tessy Thomas, the Missile Woman of India, Inspires Graduating Students

Read More

IIT Delhi to Hold 56th Convocation on August 2, 2025; the Missile Woman of India, Dr. Tessy Thomas, to be the Chief Guest

Read More

Workshop on ‘Future Ready Energy Education: Opportunities and Challenges’ Held at IIT Delhi

Read More

Change Makers 2025 Summer Bootcamp Successfully Culminates at IIT Delhi with High School and 1st Year UG Students Presenting Promising Innovative Solutions to Environmental Challenges

Read More

QS World University Rankings 2026: IIT Delhi Features in List of Top 125 World Institutions; Emerges as No. 1 Educational Institute in India

Read More

Breakthrough: IIT Delhi Researchers Develop a Multifunctional Optoelectronic Computing Device (MOD-PC) for Next-Gen Neuromorphic Hardware

Read More

IIT Delhi and LG Electronics Partner to Drive Innovation in Sustainable Home Appliance Technologies

Read More

World Environment Day 2025 Celebrated at IIT Delhi; Institute Highlights Need for Collective Action

Read More

IIT Delhi launches new undergraduate programme BS in Chemistry for JEE (Advanced) 2025 qualified candidates

Read More

Central Electricity Regulatory Commission, IIT Delhi and Grid Controller of India Sign MoU to Establish Centre of Excellence for Regulatory Affairs in Power Sector

Read More

HORIBA India Join Hands with IIT Delhi to Support Three Technical Development Research Projects

Read More

IIT Delhi Hosts ‘Manasvi: STEM Mentorship Program for High School Girls’ – Empowering Young Girls with Exposure and Opportunities to Become Future-Ready for STEM

Read More

IIT Delhi Debuts Online Post Graduate Diplomas to Empower Next-Gen Technological Leadership

Read More

Manufacturing Innovation Show: Agricultural Machineries, On-road Power Generation Device Among Several Prototypes Developed by 1st Year IIT Delhi UG Students

Read More

IIT Delhi Establishes a Chair on Applied AI for Sustainable Systems in Collaboration with R Systems

Read More

Fuelling a Sustainable Future: IIT Delhi-Abu Dhabi Announces Second Intake for Post-Graduate Energy & Sustainability Programs

Read More

IIT Delhi Successfully Conducts CAIC Student Elections Through E-Voting, Eyes Scaling to Larger Platforms

Read More

IIT Delhi, Central Water Commission Sign MoU for Water Resources Management Through Data Science, AI and Machine Learning

Read More

IIT Delhi Celebrates the Legacy of Dr. B.R. Ambedkar with “Jai Bhim Saptah” – A Week of Reflection, Dialogue, and Action

Read More

आईआईटी दिल्ली का ‘उन्नति एआई एक्सेलरेटर’ लॉन्च | Microsoft and FITT IIT Delhi Launch Unnati AI Accelerator to Drive AI-led Social Impact in Tier-II and Tier-III Towns of India

Read More

Placement 2024-25: UG Students at IIT Delhi Secure 850 Unique Offers to Date, Highest in Last Three Years

Read More

Empowering the Future: Through NURTURE Program IHFC (TIH of IIT Delhi) Trains Over 50,000 SC/ST Students in Cutting-Edge Technologies

Read More

IIT Delhi Invites Applications from High Schoolers and 1st Year UG Students for Change Makers 2025 Summer Bootcamp

Read More

JAM Admission Portal JOAPS for Various Master’s Programs in IITs to Open from March 26, 2025

Read More

IIT Delhi organises ‘Anveshan 2025’ as a part of the Institute’s initiative of “Experience IITD”

Read More

International Happiness Day Celebration marks the inauguration of Rekhi Mind Lab at IIT Delhi to promote Happiness Studies

Read More

New Zealand Prime Minister Strengthens Academic Ties with India, Announces Scholarships at IIT Delhi

Read More

QS World University Rankings by Subject 2025: IIT Delhi Features Among Top 30 World Institutions in Engineering & Technology Category

Read More

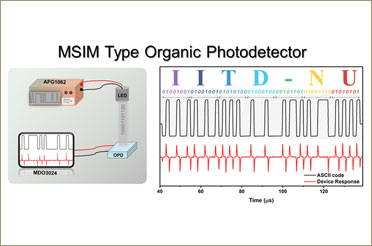

IIT Delhi Researchers Develop High-Speed, Self-Powered Photodetector for Next-Gen Optical Communication

Read More

IIT Delhi to Organise an Insightful Event, “Anveshan: Innovation and Exploration Across Disciplines”, for Undergraduate and Postgraduate Students, Showcasing Curriculum, Research, and Campus Life

Read More

SANGAM, An Inclusive Intercollege Sports Event for Students with Disabilities, Held at IIT Delhi

Read More

Bhagwan Birsa Munda Cell at IIT Delhi Hosts an Exposure Visit for 200 Tribal Students from Five States

Read More

IIT Delhi and The University of Queensland Invite Applications for Joint PhD Programme to Begin in July 2025

Read More

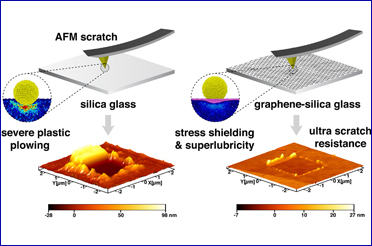

Invisible Armor: Study Shows Atomically Thin Graphene Shields Glasses from Simultaneous Mechanical and Chemical Damage Under Water

Read More

IIT Delhi Opens Its Doors to Teachers from Technical Institutions in Haryana for Skill Enhancement and Research-Driven Learning

Read More

IIT Delhi, IndiGo Sign MoU to Drive Innovation and Create Impactful Solutions for Airline Industry

Read More

IIT Delhi and University of Exeter, UK, Host Joint Symposium on Sports Healthcare Science and Engineering

Read More

2nd Transformative Leadership in STEMM (TLS) Workshop for Ph.D. Scholars from SC/ST Community Held at IIT Delhi

Read More

IHFC Collaborates with 10 Leading Institutions Across India to Launch Transformative Co-Innovation Centres (CiC) in Deep Tech, AI and Robotics

Read More

150 High School Students Attend Inaugural Lecture Under “Sci-Tech Spins” Lecture Series 2025 at IIT Delhi

Read More

NISHAAN 2025, a Cultural Event Celebrating Diversity and Talent of Students with Disabilities, Organised at IIT Delhi

Read More

Third Batch of IIT Delhi’s STEM Mentorship Program for High School Girls Successfully Concludes

Read More

IIT Delhi Hosts Mr. Amandeep Singh Gill, UN Under-Secretary-General for Digital and Emerging Technologies and Secretary-General's Envoy on Technology, For a Discussion on AI Governance

Read More

Jake Sullivan, USA’s National Security Advisor, Delivers a Talk on 'The United States and India: Building a Shared Future' at IIT Delhi

Read More

DRDO Industry Academia-Center of Excellence (DIA-CoE) at IIT Delhi Transfers Technology of ABHED, a Light Weight Bulletproof Jacket, to three Indian Industries

Read More

IIT Delhi Students Are Choosing Diverse Career Paths, Shows the Graduation Exit Survey 2024

Read More

DFPD Launches ‘Anna Chakra’ PDS Supply Chain Optimization Tool Developed by PSL, IIT Delhi

Read More

IIT Delhi Leads Landmark Collaboration with Hyundai Motor Group to Advance Battery and Electrification Research

Read More

Bhagwan Birsa Munda Cell at IIT Delhi Hosts Commemoratives Events on Janjatiya Gaurav Diwas

Read More

AIIMS New Delhi, IIT Delhi and UCL Announce Trilateral Partnership to Scale Up MedTech Innovation

Read More

AIIMS New Delhi, IIT Delhi and UCL Announce Trilateral Partnership to Scale Up MedTech Innovation

Read More

IIT Delhi and Centre for Railway Information Systems Partner to Transform Indian Railways Through Cutting-Edge Research

Read More

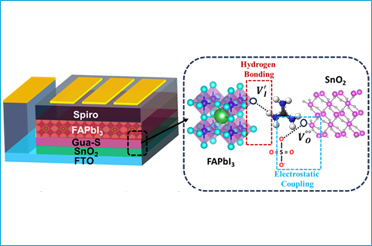

IIT Delhi Researchers Find a Potential Solution to Develop Perovskite Solar Cells Under Air Ambient Conditions Without Using Anti-Solvents

Read More

AI to Empower, Not Threaten: Meta's Chief AI Scientist Yann LeCun Calls for New Model Architectures at IIT Delhi

Read More

IIT Delhi Launches MS (Research) Program in ‘Healthcare Technology’ for Medical and Allied Clinical Professionals

Read More

Workshops Organised for Parents and School Kids to Raise Awareness and Co-Create Possible Solutions to Beat the Heat

Read More

IIT Delhi, IAF Join Hands for AI-powered Research on Technical Textiles; to Focus on Parachute and Other Safety Equipment

Read More

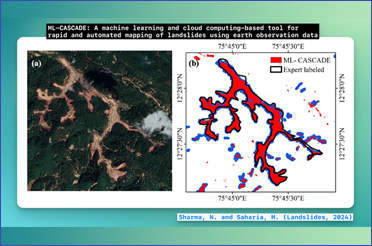

IIT Delhi Researchers Develop and Release a Machine Learning and Cloud Computing Based Tool for Rapid and Automated Mapping of Landslide Extent

Read More

Researchers at IIT Delhi Demonstrate a New Polymeric Material Having Potential to Develop Advanced Electronic Devices for Data Storage and Encryption

Read More

India's first-of-its-kind DST Supported CO2-to-Methanol Pilot Plant Project to be Implemented by IIT Delhi and Thermax Ltd. in PPP Mode

Read More

IIT Delhi and Systra Group Sign MoU to Collaborate on Research Advancing Sustainable Development Goals

Read More

Joint Admission Test for Masters (JAM) 2025: Application window opens on 3rd September 2024

Read More

Rashtriya Vigyan Puraskar 2024: Prof. Bhim Singh, SERB National Science Chair and Emeritus Professor at IIT Delhi, Honored with the Vigyan Shri Award

Read More

IIT Delhi Researchers Find a Potential Solution to Regulate Dendrite Growth in Room-Temperature Sodium-Sulfur Batteries

Read More

IHFC (TIH of IIT Delhi), and AIIMS’ SET Facility Partner to Advance Medical Innovation with “Medical Cobotics Centre” in New Delhi

Read More

IIT Delhi to Hold its 55th Convocation on August 10, 2024; Shri. Hari S. Bhartia, Founder and Co-Chairman, Jubilant Bhartia Group to be Chief Guest

Read More

IIT Delhi Develops Two Pioneering Healthcare Technologies; Successfully Transfers them to Industry

Read More

‘Green Tech Accelerator 2024 - an initiative to empower growth-stage startups under the SIDBI Cluster Intervention Program in association with ReNew and FITT, IIT Delhi

Read More

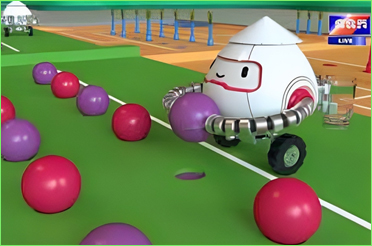

DD Robocon India 2024: Nirma University from Gujarat Wins Robotics Competition; Maharashtra’s Pimpri Chinchwad College of Engineering Secures Runner-up Position

Read More

IIT Delhi Scientists Working on Cure for Brain Cancer Gets Promising Results in Pre-Clinical Trials

Read More

Initiative for Gender Equity and Sensitisation (IGES) at IIT Delhi to Organise Wikipedia Edit-a-Thon on July 5

Read More

Bridging the Gap: IIT Delhi’s Aab Prahari App Enables Citizens to Report Real-Time Flooding Incidents and Help Civic Agencies During Monsoon

Read More

National Centre for Assistive Health Technologies (NCAHT) at IIT Delhi Launches Assistive Technology Products for Visually Challenged

Read More

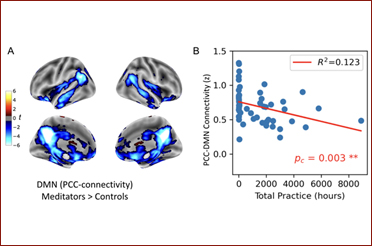

First-Ever Brain Imaging Study on Yoga Nidra Finds Significant Changes in the Brain’s Functional Connectivity during the Practice

Read More

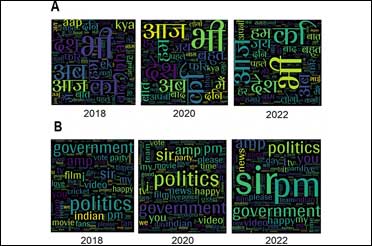

Hinglish Helps Users Engage More Effectively with a Broader Audience On Social Media: Study

Read More

An Open House for All JEE (Advanced) 2024-Qualified Candidates Aspiring to Join IIT Delhi’s Hauz Khas Campus in India or Abu Dhabi Campus in UAE to be Organised on June 15, 2024

Read More

Students Clearing JEE Advanced 2024 can apply for Admissions to IIT Delhi-Abu Dhabi Campus

Read More

Entrepreneurship Development Cell at IIT Delhi Collaborates with Alumni to Conduct an Entrepreneurship Course for Students on Building Successful Startups from Scratch

Read More

IIT Delhi’s Technology Innovation Hub IHFC, ITU Collaborate to Organise ‘Robotics for Good Youth Challenge’

Read More

QS World University Rankings by Subject 2024: IIT Delhi Ranked Among the Top 100 World Institutions in 08 Specific Subject Areas; Features Among Top 50 in Engineering and Technology

Read More

IIT Delhi Researchers Develop Highly Efficient Terahertz Radiation Source for Beyond 6G Technology

Read More

Antara Senior Care Signs MoU with IIT Delhi to Design Innovative Mobility-aid Solutions for Seniors

Read More

Israel Aerospace Industries and IIT Delhi Sign CSR Agreement to Collaborate on Applied Research

Read More

IIT Delhi’s Department of Humanities and Social Sciences to Offer a New Academic Program ‘M.A. in Culture, Society, Thought’

Read More

Bill Gates Inspires IIT Delhi Students, Encourages Them to Apply Their Skills to Global Challenges

Read More

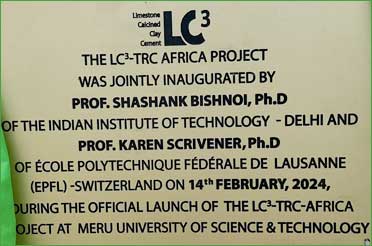

LC3-TRC Africa Project Mentored by IIT Delhi Researchers Inaugurated at Kenya’s Meru University of Science and Technology

Read More

R Systems International Ltd. and IIT Delhi Partner to Set Up a Centre of Excellence on Applied AI for Sustainable Systems

Read More

Transformative Leadership in STEMM (TLS) Workshop for Ph.D. Scholars from SC/ST Community Held at IIT Delhi

Read More

Oil India Limited in Collaboration with FITT, IIT Delhi Launches ‘DriftTECH’, an Innovation Program for Empowering Entrepreneurs and Visionaries to Address Real-world Problems!

Read More

IIT Delhi Launches a New Academic Program ‘M.Sc. in Biological Sciences’; Admissions Through JAM

Read More

GRIP: IIT Delhi Students Visit Uttarakhand Villages; Will Develop Tech Solutions to Address Issues Faced by Local Population

Read More

National Service Scheme (NSS) of IIT Delhi Launches an In-house-developed Mobile App, Making Volunteering Much More Accessible

Read More

A Study by IIT Delhi Researchers Proposes Solutions for Fair Compensation to Food Delivery Agents in India

Read More

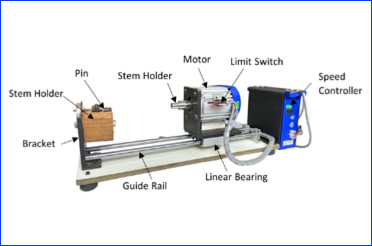

Rural Technology Action Group at IIT Delhi Transfers “AC Motor-Powered Wooden Bead Making Device” Fabrication Technology to Industry

Read More

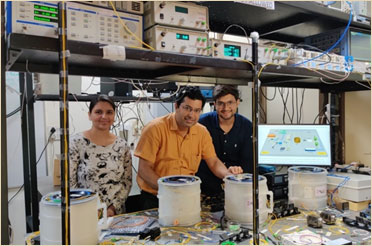

Researchers Develop Real-Time Bioelectrochemical Sensor for Rapid Water Quality Monitoring

Read More

IIT Delhi Faculty Combines Technology with Art Forms to Offer a Holistic Educational Experience to Materials Engineering Students

Read More

Placement Season Begins at IIT Delhi- Students Receive 480 Job Offers By the End of December 1

Read More

Over 30 High School Girls Successfully Complete Second STEM Mentorship Program Launched by IIT Delhi

Read More

IIT DELHI ANNOUNCES M. TECH. IN ENERGY TRANSITION AND SUSTAINABILITY FOR THE ABU DHABI CAMPUS: Last date extended to November 30, 2023

Read More

IIT Delhi Researchers Find Ultrathin Graphene Coating Can Make Glasses Extremely Scratch-Resistant

Read More

Hon'ble Vice-President of India, Shri Jagdeep Dhankhar, Visits IIT Delhi and Interacts with Students

Read More

Tehri Hydro Development Corporation India Limited (THDCIL) and IIT Delhi Ink MoU for Transformative Research and Development Initiatives

Read More

DAKSH Centre of Excellence for Law and Technology at IIT Delhi Launches a Book Titled ‘Technology and Analytics for Law and Justice’

Read More

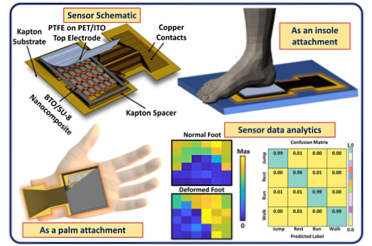

IIT Delhi Researchers Develop Scalable Wearable Pressure Sensor That Can Help Doctors and Specialists Analyze Gait Patterns and Postural Deformities

Read More

Researchers at IIT Delhi Achieve Trusted-node-free Secure Quantum Communication for 380 km in Standard Telecom Fiber

Read More

First of Its Kind ‘Medical Cobotics Centre (MCC)’ Inaugurated in New Delhi; to Foster Innovation in Healthcare

Read More

IIT Delhi and EXL Enter into MoU to Work Towards Empowering Women Entrepreneurs Through Digital and Financial Literacy

Read More

IIT Delhi's Exoskeleton Device Heads for International Footprint to Australia for Clinical Trials in Collaboration with Proxmed

Read More

Raised Lines Foundation Launches Tactile STEM Learning Kit for Visually Impaired Children on its 5th Anniversary

Read More

IIT Delhi's School of Public Policy Successfully Places its Inaugural Masters in Public Policy Batch

Read More

Workshop on MedTech and Healthcare Ecosystem for Upcoming IIT Delhi - Jhajjar Campus Organised

Read More

2357 Graduating IIT Delhi Students Receive Degrees and Diplomas at the 54th Annual Convocation Ceremony

Read More

IIT Delhi to Hold its 54th Convocation on August 12; Eminent Virologist Dr. Gagandeep Kang to be the Chief Guest

Read More

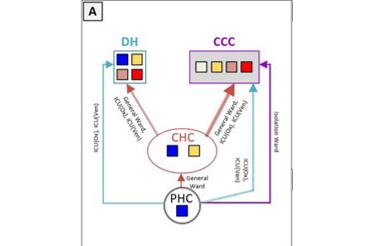

Researchers Develop a Simulation Tool for Planning Operational Response During a Health Crisis

Read More

IIT Delhi to Organise Open House on June 24 for JEE (Advanced) 2023 Qualified Female and PwD Candidates

Read More

AI/ML Model Developed by IIT Delhi-led Researcher Predicts 2023 to be a Normal Monsoon Year

Read More

Researchers at IIT Delhi Develop Mobile Robot “Robomuse 5.0” Capable of Carrying Payloads Up to 100 kg

Read More

IIT Delhi Celebrates World Telecommunication Day; India’s G20 Sherpa, Mr. Amitabh Kant, Delivers Annual Bharti Lecture

Read More

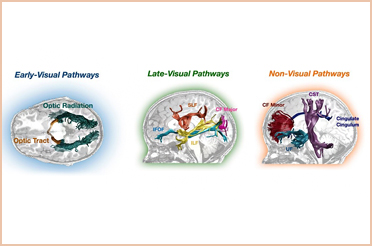

Evidence of Structural Brain Plasticity Observed Following Treatment to Congenital Blind Humans

Read More

MechAnalyzer Software to Help Engineering Students Learn Concepts of Mechanisms; FITT-IIT Delhi and SVR InfoTech Sign MoU for Sale and Tech Support

Read More

Venus Chair Established at IIT Delhi to Support Teaching and Research & Development in the Area of Fibrous Air Filters

Read More

IIT Delhi’s Two-Day Annual Career Fest ‘Pravritti 2023- Expanding Horizons’ to Begin on April

Read More

QS World University Rankings by Subject 2023: IIT Delhi Among the Top 50 Institutions in the World in Engineering & Technology with 48th Rank

Read More

MoS for Education Dr. Subhas Sarkar Inaugurates Unnat Bharat Abhiyan's "UNNATI Mahotsav and Expo" at IIT Delhi

Read More

Hon’ble Australian Prime Minister Mr. Anthony Albanese Visits IIT Delhi; Addresses Students

Read More

IIT Delhi’s Three-day Annual Science, Technology and Management Festival “Tryst 2023” Kicks Off

Read More

Researchers at IIT Delhi and IIT Bombay Develop Highly Efficient Spintronics-Based Neuromorphic Hardware

Read More

IIT Delhi Alumnus Alok Aggarwal Endows Chair for Research in ESG (Environmental, Social, and Governance) Area

Read More

IIT Delhi to Develop Smart Monitoring System to Ensure Safety of Persons Working at Height

Read More

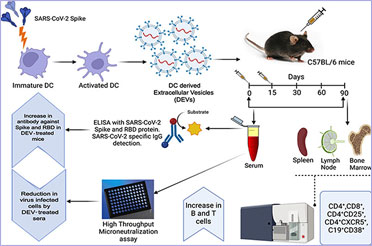

Researchers' Efforts to Develop a Next-Generation Vaccine Against COVID-19 Give Promising Results in Animal Trial Phase

Read More

Technology Innovation Hub of IIT Delhi “IHFC” Plans to Train Students From 100+ Schools in Delhi on Robotics in Next Two Months

Read More

Mobility for All: Continental with IIT Delhi Develop A Solution for Visually Impaired To Access Public Buses

Read More

IIT Delhi Placement Drive 2022-23: Students Receive Record Number of Job Offers Up to December 15

Read More

IIT Delhi and University of Helsinki, Finland, Sign MoU for Academic Cooperation; Aims to Contribute to Solving Air Quality and Climate Change Challenges in India

Read More

Four Startups led by IIT Delhi Students Win a Grant of Rs 50 lakh Each Under Endowment Nurture Fund Initiative

Read More

IIT Delhi Holds 53rd Annual Convocation Ceremony; 2100 Graduating Students Awarded Degrees and Diplomas

Read More

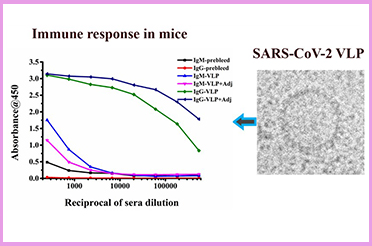

Researchers Led by IIT Delhi Scientist Develop a VLP-based Vaccine Candidate Against COVID-19

Read More

IIT Delhi Showcases Technologies with Societal Impact, Innovations in Clean Energy, Healthcare, Manufactuting at All IITs R&D Fair IInvenTiv

Read More

Rural Technology Action Group (RuTAG) at IIT Delhi Transfers Two Technologies to Four African Nations

Read More

IIT Delhi Launches Mobile Application ‘IITD Aab Prahari (आब प्रहरी)’ to Address Waterlogging Issues in Urban Areas During Monsoon

Read More

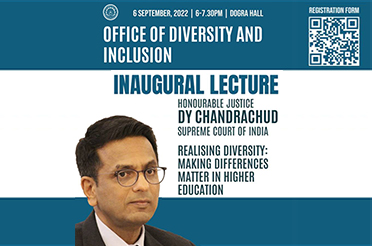

Supreme Court Judge Hon’ble Justice D.Y. Chandrachud to Deliver Inaugural Talk for the Office of Diversity and Inclusion at IIT Delhi

Read More

IIT Delhi Diamond Jubilee Celebrations Closing Ceremony- Director Prof. Rangan Banerjee's Speech

Read More

Hon’ble President of India, Smt. Droupadi Murmu Graces IIT Delhi Diamond Jubilee Celebrations Closing Ceremony

Read More

Union Minister Shri Piyush Goyal Inaugurates Public Systems Lab at IIT Delhi Established in Partnership with UNWFP

Read More

IIT Delhi’s Technology Innovation Hub IHFC Gets 12 Projects Under DST-NSF Joint Research and Development Program

Read More

IIT Delhi Researchers Propose Non-invasive, Time Efficient and Patient Friendly Diagnostic Tool for Epileptogenic Zone Detection

Read More_1659327288.jpg)

IIT Delhi Organises Academic Outreach Day for Students and Faculty of Haryana Govt. Technical Universities and Colleges

Read More

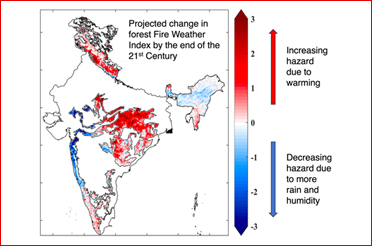

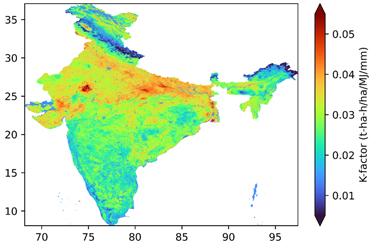

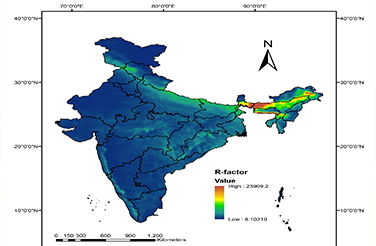

Researchers at IIT Delhi Develop Map to Highlight Areas Prone to Rainfall-induced Erosion in India

Read More

NIRF India Rankings 2022- IIT Delhi Achieves 2nd Rank in Engineering; Jumps to 4th in Management; Features Among Top 3 Research Institutes

Read More

IIT Delhi Alumni Parul and Alok Mittal Pledge to Contribute Rs 5 Cr to Institute’s Endowment Fund

Read More

Startup Incubated at IIT Delhi Develops Antimicrobial Solution That Provides Long-Lasting Protection Against Hospital-Acquired Infections

Read More

First Batch Successfully Completes IIT Delhi’s STEM Mentorship Program for High Schoolgirls

Read More

School students showcase promising prototypes they built at Change.Makers summer boot camp organised by IIT Delhi

Read More

IITs in Delhi, Bombay and Kanpur Offer Internship and Sponsored M. Tech. Programmes to Students from Ladakh

Read More

IHFC, TIH of IIT Delhi, Celebrates its 2nd Anniversary; Announces Call for Proposal in Areas of Autonomous Vehicles, Nano Robotics, Block Chain for Applications in Robotics

Read More

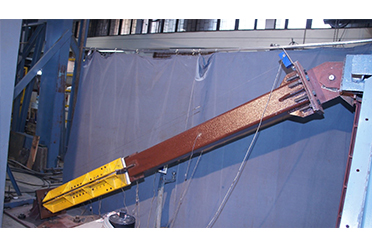

IIT Delhi Researchers Develop Low-Cost Buckling Restrained Braces That Can Improve Earthquake Resistance of Structures

Read More

Samsung Launches ‘Solve for Tomorrow’, an Innovation Contest for India’s Youth to Crack Real-World Problems; FITT at IIT Delhi to be the Knowledge Partner

Read More

QS World University Rankings 2023- IIT Delhi Achieves an Improved Overall Rank of 174 Globally

Read More

Biomass Burning Drives Poor Air Quality in Delhi Post Diwali, Not Fireworks: IIT Delhi Study

Read More

Technology Innovation Hub of IIT Delhi (IHFC) Signs MoU with the Council for the Indian School Certificate Examinations (CISCE)

Read More

Researchers Led by IIT Delhi Develop Technology to Enable Use of Environment-Friendly Dimethyl Ether as Fuel in Automotive Vehicles

Read More

Did Climate Change Cause Ancient Civilizations to Collapse? 08thIIT Delhi SciTech Spins Lecture to Explain

Read More

QS World University Rankings by Subject 2022 - Five IIT Delhi Academic Programmes in Top 100

Read More

IIT Delhi, Delhi Jal Board Sign MoU to Address Water Security Issues Faced by NCT of Delhi

Read More

World Class Indoor Sports Complex Built with Alumnus Saurabh Mittal's Support Inaugurated at IIT Delhi

Read More

Fabiosys Innovations, an IIT Delhi Startup, Develops Technology to Manufacture Extremely Affordable and Highly Effective Antiviral Fabric

Read More

IHFC, Technology Innovation Hub of IIT Delhi, Collaborates with US’ National Science Foundation for Research in Cobotics, AI

Read More

HORIBA India, IIT Delhi Join Hands to Establish Research Center at the Institute’s Chemistry Department

Read More

Troop Comforts Ltd Signs MoU with IIT Delhi to Develop Smart Protective Clothing for Indian Security Forces

Read More

IIT Delhi Researchers Design and Demonstrate a New Strategy for Development of Drug Molecules

Read More

SciTech Spins Lecture: School Students to Learn About Role of Imaging in Advancing Science and Technology

Read More

IIT Delhi Launches an Interactive Website of IIT-PAL to Help High School Students Prepare for Competitive Exams

Read More

IIT Delhi Researchers Develop High Efficiency, Shadow-less, Portable Solar PV Towers for Power Generation

Read More

IIT Delhi Sets up “Pillay Chair Professor” for Research in Machine Learning, VLSI Design and Sensors

Read More

IIT Delhi Students Receive Record Number of Job Offers Up to December 15 of Placement Drive 2021

Read More

SciTech Spins 4th Lecture: School Students to Learn About Mysteries of Universe from IIT Delhi Scientists

Read More

RT-PCR-based Assay for Identification of Omicron Variant of SARS-CoV-2 Developed at IIT Delhi

Read More

IIT Delhi’s State of the Art Research & Innovation Park Wins Prestigious Façade Project of the Year Award 2021

Read More

IntelliSmart & IIT Delhi collaborate to develop next generation Smart Grid technology solutions & capabilities

Read More

IIT Delhi Collaborates with National Law University Delhi for Ushering in Tech-empowered Justice System

Read More

IIT Delhi and Business Sweden - The Swedish Trade and Invest Council Sign MoU for Clean Air and Green Energy Collaborations

Read More

Neilom Prize 2020-21: Recent Graduates of IIT Delhi Awarded for their Work in the Field of Assistive Technology

Read More

‘Why did the Titanic Sink?’ 3rd SciTech Spins Lecture by IIT Delhi to Explain This and Many More Questions to School Students

Read More

Technology Innovation Hubs of IIT Delhi and IIIT Delhi Sign MoU to set up India’s First Medical Cobotics Centre

Read More

State-of-the-art Laboratories Inaugurated at IIT Delhi’s Centre Focusing on Electric Vehicle Technologies

Read More

IIT Delhi, AIIMS New Delhi Jointly Establish Centre for Advanced Research and Excellence in Disability & Assistive Technology (CARE-DAT), a Centre of Excellence

Read More

IIT Delhi’s School of Artificial Intelligence to Start ‘M.Tech in Machine Intelligence & Data Science (MINDS)’

Read More

IIT Delhi to Teach School Students ‘How Powerful Computers Can Help in Providing Insights into Real-Life Phenomena’

Read More

IIT Delhi Announces Scholarships and Seed Funding Programs to Mark 2nd Anniversary of its Alumni Endowment Fund

Read More

IIT Delhi Launches New UG Programme ‘B. Tech. in Energy Engineering’; JEE (Advanced) Qualified Students Eligible

Read More

Alumnus Mohit Aron Gifts USD 1 Million to IIT Delhi’s Computer Science and Engineering Department

Read More

B.Tech. Students of NIT Sikkim to be Eligible for Direct Admission to IIT Delhi’s PhD Programmes

Read More

JK Paper Signs MoU with IIT Delhi to Set Up JK Paper Centre of Excellence in Paper and Packaging

Read More

IIT Delhi Researchers Develop Catalytic Technology for Sustainable Production of Chiral Active Pharmaceutical Ingredients

Read More

IIT Delhi’s Over Rs 500 Cr State-of-the Art ‘Central Research Facility’ Now Open for Researchers from Across Country

Read More

IIT Delhi Launches Sci-Tech Spins - A Series of Weekend Seminars & Laboratory Demos for High School Students

Read More

IIT Delhi, RDSO Researchers Develop Easy to Use Train Simulation Software ‘Runtrain#’ to Help in Train Timetabling Methods

Read More

DAKSH Centre of Excellence (CoE) for Law & Technology, IIT Delhi Releases Report on Six High Court Websites

Read More

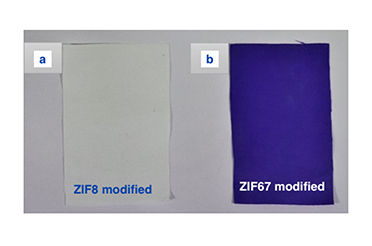

IIT Delhi Researchers Develop Modified Cotton Fabric Capable of Adsorbing Harmful Air Pollutants from Air

Read More

Vipula and Mahesh Chaturvedi Foundation Signs MoU to Attract Outstanding Talent to IIT Delhi

Read More

National Health Authority and Indian Institute of Technology Delhi join hands to scale high-potential healthcare innovations

Read More

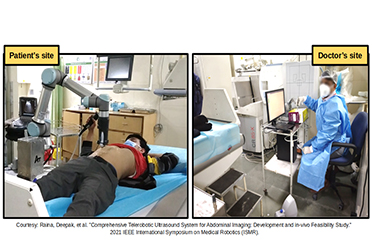

IIT Delhi, AIIMS New Delhi and Addverb Co-develop Telerobotic Ultrasound System During COVID Times

Read More

IIT Delhi Establishes Chairs to Support Research in Microelectronics & VLSI Design and Geotechnical & Geo-Environmental Engineering

Read More

IFFCO Signs MoU with IIT Delhi for Innovative & Collaborative Projects to Bring Labs to Farms

Read More

IIT Delhi Alumni Endow Indu Shrivastava & Serla Singh Chair Professor in Artificial Intelligence

Read More

IIT Delhi Startup SWATRIC Collaborates with Flag Foundation of India to Develop Advanced Textile Solution for National Flag

Read More

IIT Delhi Establishes Manish Singhal Chair to Promote Teaching and Research in the Area of Smart Textiles

Read More

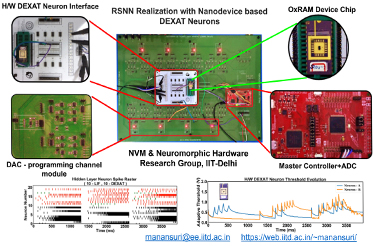

IIT Delhi Researchers Demonstrate a New Brain-inspired Artificial Neuron for Building Accurate and Efficient Neuromorphic AI Systems

Read More

Supreme Court Judge Mr. Justice S. Ravindra Bhat inaugurates UJF Lab Facility on AI for Judiciary at IIT Delhi

Read More

IIT Delhi Scientist led Research Team Develops Novel Antifungal Strategy for Fungal Eye Infection

Read More

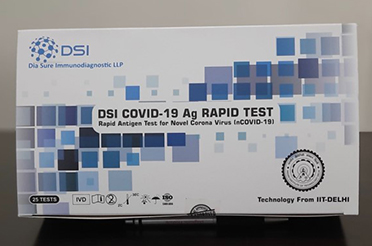

Minister of State for Education Shri Sanjay Dhotre launches the Rapid Antigen Test Kit for COVID-19 developed by IIT Delhi

Read More

Technology for Hydrogen Utilization in Spark-Ignition Engine Generator for Electricity Generation with Zero-Emission Developed by IIT Delhi Researchers

Read More

IIT Delhi to Establish Department of Energy Science and Engineering: New UG Programme B.Tech. in Energy Engineering To Be Offered from This Year

Read MoreCovid-19: IIT Delhi collaborates with Delhi Government to improve oxygen infrastructure and supply chain management in Delhi

Read More

IIT Delhi to Create New Centre to Synergize and Boost R&D Activities in Optics and Photonics Field

Read More